|

IFI High Performance Gigabit Ethernet MAC GMACII

|

|

Features

|

Protocol

|

1000 Base-T Full duplex

100 Base-TX Full duplex

|

|

Transmit Buffer (standard)

|

double buffer 2000 Byte

checksum advance logic

readback for easy software debugging

|

|

Transmit Buffer (Jumboframe support)

|

2*4, 2*8, 2*16, 2*32, 2*64 kByte

|

|

Receive Buffer (standard)

|

ring buffer, 4kByte

|

|

Receive Buffer (Jumboframe support)

|

8,16,32,64 or 128 kByte

|

|

Filter

|

MAC ID, MAC IP, IGMP

all filters can be switched off

|

|

Integrated DMA controller

|

pipelined

generates checksum on the fly

allignment aware

masteraddress support for no increment

|

|

Multicast support

|

separate MAC ID and IP filters

|

|

Avalon Interface

|

Example software included

|

|

IFI Phy Manager included

|

GMII, MII, RGMII, RMII

|

|

Reference Designs included

|

|

|

Implementation

|

Design Flows supported

|

SOPC Builder

Encrypted VHDL

|

|

Device families targeted

|

All CYCLONE families

All STRATIX families

All ARRIA families

|

|

Device resource utilization

|

~3000 LEs for CycloneIII

Ram: 8 M9K Blocks (standard buffers)

|

|

Timing Constraints

|

automatic SDC generation

|

|

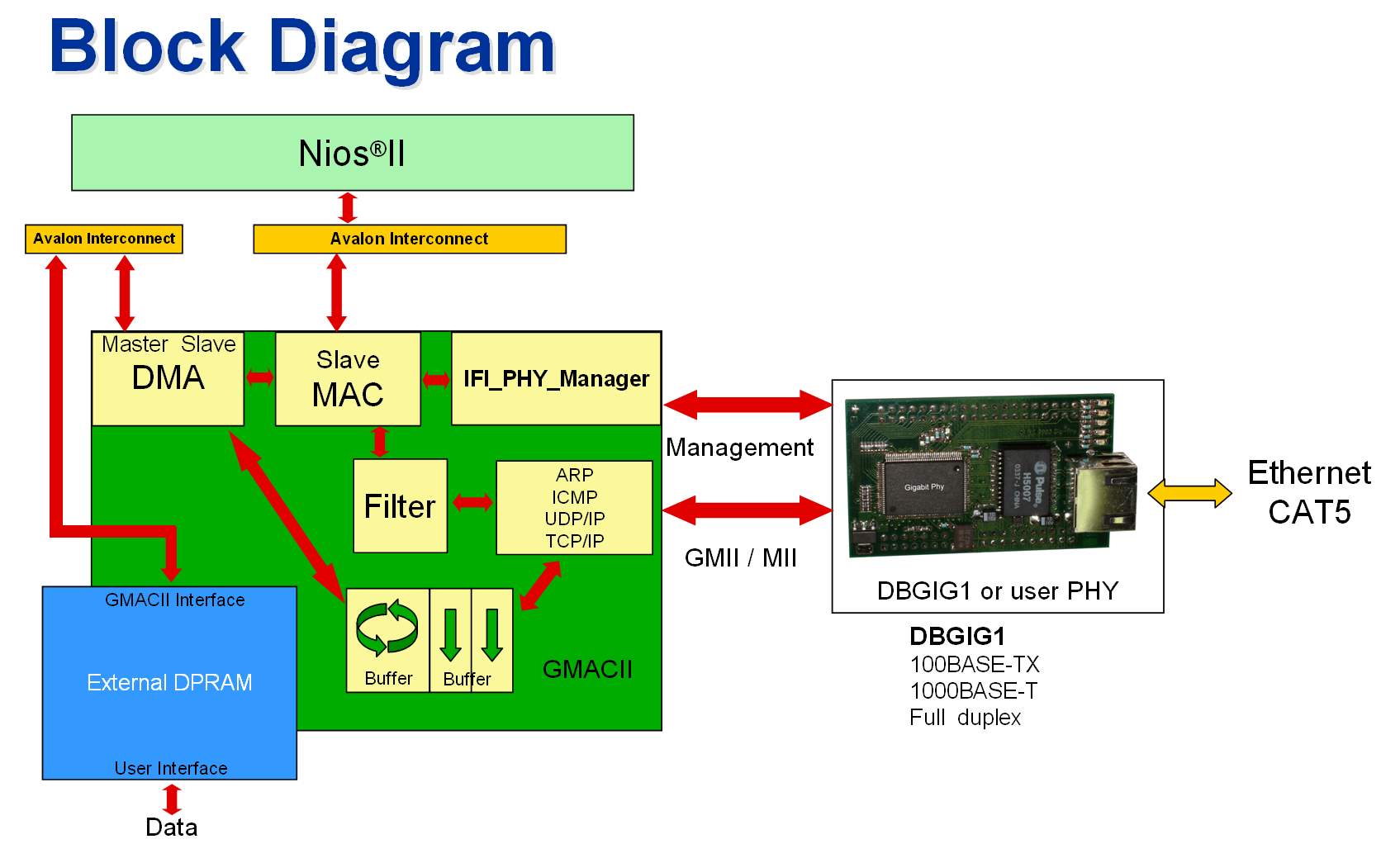

Block Diagramm

|

|